Product Summary

The GM8180SF-BD is a highly integrated H.264/MPEG-4/JPEG SoC solution targeting Internet digital video applications especially on IP surveillance and IPTV station applications. With the pure hardwired video codec architecture, the max. 500 MHz FA626 ARM-based CPU can be used for computing of audio encoding & decoding or image analysis in intelligent surveillance applications, such as object or face detection. The GM8180SF-BD is suitable for Mega-pixel IP camera, Network video recorder, Video server, Multi-channel DVR, PCI video encoder/decoder adaptors, IPTV station, Network set-top box/DVD, Digital media box and Network attached storage.

Features

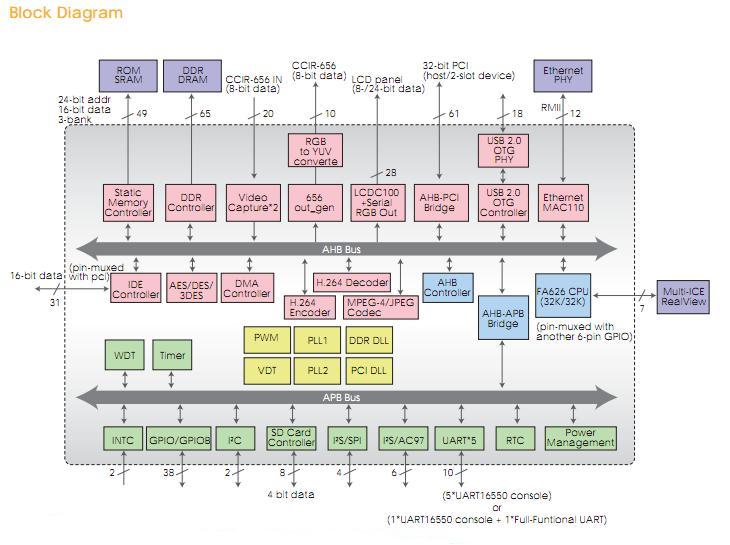

GM8180SF-BD features: (1)CPU FA626 , 500 MHz (max.), 32K I-cache/32K D-cache ( Provided by Faraday Technology ) ; (2) Memory Interface 16-/32-bit DDR SDRAM Controller up to 333 MHz/1GB 8-/16-bit static memory controller, supporting NOR-type flash memory, SRAM and ROM; (3) H.264 Codec Encoder supporting Baseline Profile, from level 1 ~ 3.1 up to D1, 75 fps Supports VBR and CBR; Decoder supporting Baseline Profile, from level 1 ~ 3.0 up to D1, 60 fps ASO or FMO not supported; (4) MPEG-4/JPEG Codec MPEG-4 supporting Simple Profile level 0 ~ 3, encoder up to D1, 60 fps or decoder up to D1, 60 fps; (5)JPEG is compliant with ISO/IEC 10918-1 baseline standard; (6)Video Capture Supports 2 ITU 656 interfaces - YUV 4:2:2 and 16-bit YUV interface Resolution: Up to 1280 x 1024 Supports noise reduction, color OSD and input scalar; (7)Display Interface ITU-656 8-bit video output, up to 720 x 480 or 720 × 576 8-/24-bit RGB interface, supporting TFT color display up to 1024 × 768 OSD with 256 programmable 12 × 16 fonts; (8)PCI Interface Compliant with PCI 2.2, up to 66 MHz Supports 2-slot PCI masters in the PCI host/device modes; (9)AES/DES/3DES Cipher Controller Hardware implementation of AES/DES/3DES algorithm with DMA functions; (10)AHB Peripherals 802.3 MAC, USB 2.0 OTG, ATA-133 IDE; (11)APB Peripherals SD 1.0/MMC 4.0 controller, timer, WDT, RTC, INTC, GPIO (16-pin), I2C, PMU, I2S, UART; (12)Operating Voltage 1.2 V (core), 2.5 V (DDR DRAM I/O) and 3.3 V (I/O) ; (13)Process UMC 0.13 μm logic process; (14)Package 484-pin BGA (23 × 23 mm2) .

Diagrams

(China (Mainland))

(China (Mainland))